Description:

Each of these monolithic counters contains four master-slave flip-flops and additional gating to provide a divide-by-two counter and a three-stage binary counter for which the count cycle length is divide-by-five for the ’90A and ‘LS90, divide-by-six for the ’92A and ‘LS92, and the divide-by eight for the ’93A and ‘LS93.

All of these counters have a gated zero reset and the ’90A and ‘LS90 also have gated set-to-nine inputs for use in BCD nine’s complement applications.

To use their maximum count length (decade, divide-by-twelve, or four-bit binary) of these counters, the CKB input is connected to the QA output. The input count pulses are applied to CKA input and the outputs are as described in the appropriate function table. A symmetrical divide-by-ten count can be obtained from the ’90A or ‘LS90 counters by connecting the QD output to the CKA input and applying the input count to the CKB input which gives a divide-by-ten square wave at output QA.

Specifications:

| Through Hole | |

| PDIP-14 | |

| LS | |

| 4 bit | |

| Up | |

| 4.75 V to 5.25 V | |

| 0 C | |

| + 70 C | |

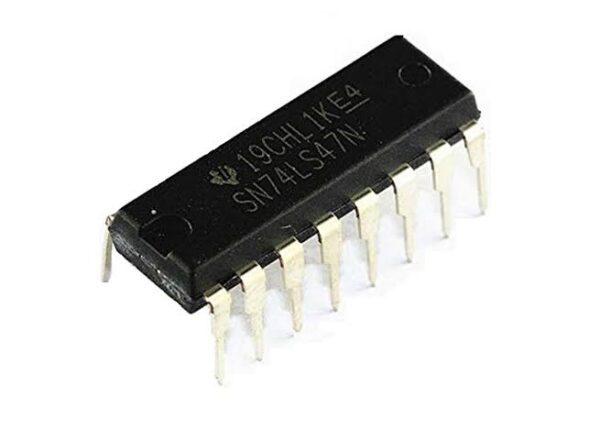

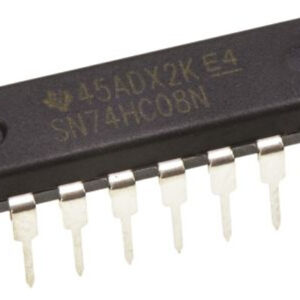

| SN74LS92 | |

| Tube | |

| Brand: | Texas Instruments |

| Function: | Counter |

| Operating Temperature Range: | 0 C to + 70 C |

| Output Current: | 8 mA/- 400 uA |

| Product Type: | Counter ICs |

Pinout Overview:

Pin Name Description

1 Q3 Output bit 3 (MSB)

2 Q2 Output bit 2

3 Q1 Output bit 1

4 Q0 Output bit 0 (LSB)

5 GND Ground

6 CP1 Clock input (divide by 2)

7 CP2 Clock input (divide by 6)

8 NC Not connected

9 MR1 Master Reset Input 1

10 MR2 Master Reset Input 2

11-13 NC or unused

14 VCC Power Supply (+5V)

Applications:

- Frequency dividers

- Digital clocks

- Timing circuits

Package Include:

1 x SN74LS92N SemiConductor IC

Reviews

There are no reviews yet.